# NMOS 6510 Unintended Opcodes

no more secrets (v0.94 - 24/12/19)

# **Contents**

| <u>Preface</u>                                               | <u>I</u>   |

|--------------------------------------------------------------|------------|

| Scope of this Document.                                      | <u>I</u>   |

| Intended Audience                                            | <u>I</u>   |

| <u>License</u> .                                             |            |

| What you get.                                                | <u>II</u>  |

| Naming Conventions                                           | <u>III</u> |

| Address-Mode Abbreviations                                   | <u>III</u> |

| Mnemonics.                                                   | <u>III</u> |

| Processor Flags                                              | <u>IV</u>  |

| Unintended Opcodes                                           | <u>1</u>   |

| <u>Overview</u> .                                            | <u>1</u>   |

| <u>Types</u>                                                 | <u>3</u>   |

| Combinations of two operations with the same addressing mode | <u>3</u>   |

| Combinations of an immediate and an implied command.         | <u>3</u>   |

| Combinations of STA/STX/STY                                  |            |

| Combinations of STA/TXS and LDA/TSX                          | <u>4</u>   |

| No effect                                                    | <u>4</u>   |

| Lock-up.                                                     | <u>4</u>   |

| Stable Opcodes.                                              | <u>5</u>   |

| SLO (ASO)                                                    | <u>5</u>   |

| Example: Multibyte left shift and load leftmost byte         | <u>6</u>   |

| RLA (RLN)                                                    | <u>7</u>   |

| Example: scroll over a background layer.                     | <u>8</u>   |

| Example: multiply by 3, 5, 7, 10                             | <u>8</u>   |

| SRE (LSE).                                                   |            |

| Example: 8bit 1-of-8 counter                                 | <u>10</u>  |

| RRA (RRD).                                                   | <u>11</u>  |

| Example: noise LFSR                                          | <u>12</u>  |

| SAX (AXS, AAX)                                               | <u>13</u>  |

| Example: store values with mask.                             | <u>14</u>  |

| Example: update Sprite Pointers.                             | <u>14</u>  |

| <u>LAX</u>                                                   | <u>15</u>  |

| Example: load A and X with same value.                       | <u>16</u>  |

| DCP (DCM)                                                    | <u>17</u>  |

| Example: decrementing loop counter                           | <u>18</u>  |

| Example: decrementing 16bit counter.                         | <u>18</u>  |

| ISC (ISB, INS)                                               | <u>19</u>  |

| Example: incrementing loop counter.                          |            |

| Example: increment indexed and load value.                   | <u>20</u>  |

| ANC (ANC2, ANA, ANB)                                         | <u>21</u>  |

| Example: implicit enforcement of carry flag state            |            |

| Example: remembering a bit.                                  | <u>22</u>  |

| ALR (ASR)                                                    |            |

| Example: right shift and mask                                |            |

| Example: fetch 2 bits from a byte.                           | <u>24</u>  |

| Example: add offset depending on LSB.                        | <u>24</u>  |

| <u>ARR</u>                                                   |            |

| Example: rotating 16 bit values.                             | <u>26</u>  |

| Example: load register depending on carry.                   | 27         |

# Contents

| Example: shift zeros or ones into accumulator.    | <u>27</u> |

|---------------------------------------------------|-----------|

| SBX (AXS, SAX, XMA)                               | <u>28</u> |

| Example: decrement X by more than 1               | <u>29</u> |

| Example: decrement nibbles.                       |           |

| Example: apply a mask to an index.                |           |

| SBC (USBC, USB).                                  |           |

| LAS (LAR)                                         |           |

| Example: cycle an index within bounds             |           |

| NOP (NPO, UNP).                                   |           |

| NOP (DOP, SKB)                                    |           |

| NOP (TOP, SKW).                                   |           |

| Example: acknowledge IRQ.                         |           |

| JAM (KIL, HLT, CIM, CRP).                         |           |

| Example: stop execution.                          |           |

| Unstable Opcodes.                                 |           |

| 'unstable address high byte' group                |           |

| SHA (AXA, AHX, TEA).                              |           |

| Example: SAX abs, y                               |           |

| Example: SAX (zp), y.                             |           |

| SHX (A11, SXA, XAS, TEX)                          |           |

| Example: STX abs, y.                              |           |

| SHY (A11, SYA, SAY, TEY).                         |           |

| Example: STY abs, x.                              |           |

| TAS (XAS, SHS).                                   |           |

| Example: SAX abs, y with SP=A & X.                |           |

| 'Magic Constant' group                            |           |

| ANE (XAA, AXM)                                    |           |

| Example: clear A                                  |           |

| $\overline{\text{Example: A = X AND immediate}}.$ |           |

| Example: read the 'magic constant'                |           |

| LAX #imm (ATX, LXA, OAL, ANX)                     |           |

| Example: clear A and X                            |           |

| Example: load A and X with same value.            |           |

| Example: read the 'magic constant'                |           |

| Unintended addressing modes.                      |           |

| Absolute Y Indexed (R-M-W).                       |           |

| Zeropage X Indexed Indirect (R-M-W)               | 56        |

| Zeropage Indirect Y Indexed (R-M-W)               |           |

| Unintended decimal mode                           |           |

| Decimal mode in a nutshell                        |           |

| invalid BCD.                                      |           |

| affected instructions.                            | <u>61</u> |

| <u>ADC</u>                                        | <u>61</u> |

| Example: convert a hex digit to ASCII             |           |

| Example: convert a hex digit to BCD.              |           |

| Example: Distinguish NMOS 6502 from CMOS 65C02.   |           |

| SBC (USBC)                                        |           |

| <u>ARR</u> .`                                     | <u>66</u> |

| ISC (ISB, INS)                                    | <u>67</u> |

| RRA (RRD)                                         | 68        |

# **Contents**

| <u>Unintended bugs and quirks</u> .      | <u>69</u> |

|------------------------------------------|-----------|

| Zeropage addressing modes & page wraps.  | <u>69</u> |

| Indirect addressing mode & page wraps.   |           |

| Appendix.                                | _ ~       |

| Opcode naming in different Assemblers.   | 70        |

| Combined Examples.                       |           |

| negating a 16bit number.                 | <u>71</u> |

| a smart addition.                        |           |

| Multiply 8bit * 2 ^ n with 16bit result. |           |

| 6 sprites over FLI.                      |           |

| Blackmail FLI                            |           |

| References.                              |           |

| Greets and Thanks                        |           |

| Wanted                                   |           |

| History                                  |           |

|                                          |           |

#### **Preface**

'Back in the days' so called 'illegal' opcodes were researched independently by different parties, and detail knowledge about them was considered 'black magic' for many conventional programmers. They first appeared in the context of copy protection schemes, so keeping the knowledge secret was crucial.

When some time later some of these opcodes were documented by various book authors and magazines, a lot of misinformation was spread and a number of weird myths were born. It took another few years until some brave souls started to systematically investigate each and every opcode, and until the mid 90s that Wolfgang Lorenz came up with his test suite that finally contained elaborated test programs for them.

Still, a few opcodes were considered witchcraft for a while (the so called 'unstable' ones), until other people finally de-capped an actual CPU and solved the remaining riddles.

This document tries to present the current state of the art in a readable form, and is in large parts the result of pasting existing documents together and editing them (see References)

24/12/19 groepaz/solution

## Scope of this Document

To make things simple, the rest of this document refers specifically to the MOS6510 (and the CSG8500) in the Commodore 64, and to the CSG8502 found in the Commodore 128.

However, most of the document applies to MOS6502 as well. Also MOS Technology licensed Rockwell and Synertek to second source the 6502 microprocessor and support components, meaning they used the same masks for manufacturing, so their chips should behave (exactly) the same. The 6502C "Sandy" found in Atari 8-bit computers also seems to work the same.

Some of the 'unstable' opcodes are known to work slightly different on 6502 equipped machines, but that is just the result of the RDY line not being used in them.

This document does **not** apply to the 65C02, 652SC02, 65CE02, 65816 etc. (These are all not 100% 6502 compatible)

Whether related CPUs like the 7501/8501 used in the CBM264 series behaves the same has not been tested (but is likely – feedback welcomed).

#### Intended Audience

This document is not for beginners (such as yourself) \*. The reader should be familiar with 6502 assembly, and in particular is expected to know how the regular opcodes and CPU flags work exactly. For those that do not feel confident enough, having a reference to the regular opcodes, flags behaviour and things like decimal mode at hand is probably highly recommended.

\*) Wording change suggested by Poopmaster

#### License

This documentation is free as in free beer. All rights reversed.

If using the information contained here results in ultra realistic smoke effects and/or loss of mental health, it is entirely your fault. *You have been warned*.

# What you get

- Reference chart of all 'illegal' opcodes

- Cycle by cycle breakdown of the 'illegal' addressing modes

- For every 'illegal' opcode:

- Formal description of each opcode, including flags etc.

- General description of operation and eventual quirks

- o equivalent 'legal' code

- All documented behaviour backed up by test code. The referenced test code can be found in the VICE test-programs repository at

- http://vice-emu.svn.sourceforge.net/viewvc/vice-emu/testprogs/

- examples for real world usage, if available

- Some hints on using decimal mode in (not only) unintended ways

- A short description of all other unintended bugs and quirks of the CPU

# **Naming Conventions**

| Α        | Accumulator                                                 |

|----------|-------------------------------------------------------------|

|          | Accumulator                                                 |

| X        | X-register                                                  |

| Υ        | Y-register                                                  |

| SP       | Stack-pointer                                               |

| PC       | Program Counter                                             |

| NV-BDIZC | Flags in the status-register                                |

| {imm}    | An immediate value                                          |

| {addr}   | Effective address given in the opcode (including indexing)  |

| {H+1}    | High byte of the address given in the opcode, plus 1        |

| {CONST}  | 'Magic' chip and/or temperature dependent constant value    |

| &        | Binary AND                                                  |

| [        | Binary OR                                                   |

| ۸        | Binary XOR                                                  |

| +        | Integer Addition                                            |

| -        | Integer Subtraction                                         |

| *        | Integer Multiplication (powers of two work like a bitshift) |

| /        | Integer Division (powers of two work like a bitshift)       |

In the various tables colours GREEN, YELLOW and RED are used in the following way:

GREEN indicates all completely stable opcodes, which can be used without special precautions, YELLOW marks partially unstable opcodes which need some special care and RED is reserved for the remaining few which are highly unstable and can only be used with severe restrictions.

#### **Address-Mode Abbreviations**

| AA  | Absolute Address      |

|-----|-----------------------|

| AAH | Absolute Address High |

| AAL | Absolute Address Low  |

| DO  | Direct Offset         |

#### **Mnemonics**

This document lists all previously used mnemonics for each opcode in the headlines of their description, and then one variant which the author was most familiar with is used throughout the rest of the text. A table that shows which mnemonics are supported by some popular assemblers can be found in the appendix.

# **Processor Flags**

Standard notation is used for the processor flags:

| N | Negative                              |

|---|---------------------------------------|

| V | oVerflow                              |

| - | bit5 of the status register is unused |

| В | Break                                 |

| D | Decimal                               |

| I | Interrupt                             |

| Z | Zero                                  |

| С | Carry                                 |

To indicate what processor flags are used and/or modified by the respective instructions this document uses a slightly different notation than many other existing ones. In particular this will allow to indicate directly in the tables whether an instruction depends on, modifies, or just sets a flag.

| i | The instruction depends on this flag (takes it as INPUT) but does not change it. In this document this applies to the decimal flag only.                                                                  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| О | The instruction does not depend on this flag, but does set or clear it (it is OUTPUT only). The zero flag is a typical example for this (only branches depend on it, other instruction would only set it) |

| X | The instruction depends on this flag, and does change it too. The carry flag is a typical example for this (although not generally in all instructions).                                                  |

|   | The instruction does not depend on, nor change, this flag                                                                                                                                                 |

# **Unintended Opcodes**

# Overview

| Opc. | imp | imm  | zp   | zpx  | zpy  | izx  | izy  | abs  | abx  | aby  | Function                                | N | ٧ | - | В | D | I | Z | С |

|------|-----|------|------|------|------|------|------|------|------|------|-----------------------------------------|---|---|---|---|---|---|---|---|

| SL0  |     |      | \$07 | \$17 |      | \$03 | \$13 | \$0F | \$1F | \$1B | {addr} = {addr} * 2<br>A = A or {addr}  | 0 |   |   |   |   |   | 0 | 0 |

| RLA  |     |      | \$27 | \$37 |      | \$23 | \$33 | \$2F | \$3F | \$3B | {addr} = rol {addr}<br>A = A and {addr} | 0 |   |   |   |   |   | 0 | x |

| SRE  |     |      | \$47 | \$57 |      | \$43 | \$53 | \$4F | \$5F | \$5B | {addr} = {addr} / 2<br>A = A eor {addr} | 0 |   |   |   |   |   | 0 | 0 |

| RRA  |     |      | \$67 | \$77 |      | \$63 | \$73 | \$6F | \$7F | \$7B | {addr} = ror {addr}<br>A = A adc {addr} | 0 | 0 |   |   | i |   | 0 | х |

| SAX  |     |      | \$87 |      | \$97 | \$83 |      | \$8F |      |      | {addr} = A & X                          |   |   |   |   |   |   |   |   |

| LAX  |     |      | \$A7 |      | \$B7 | \$A3 | \$B3 | \$AF |      | \$BF | A,X = {addr}                            | 0 |   |   |   |   |   | 0 |   |

| DCP  |     |      | \$C7 | \$D7 |      | \$C3 | \$D3 | \$CF | \$DF | \$DB | {addr} = {addr} - 1<br>A cmp {addr}     | 0 |   |   |   |   |   | 0 | 0 |

| ISC  |     |      | \$E7 | \$F7 |      | \$E3 | \$F3 | \$EF | \$FF | \$FB | {addr} = {addr} + 1<br>A = A - {addr}   | 0 | o |   |   | i |   | 0 | х |

| ANC  |     | \$0B |      |      |      |      |      |      |      |      | A = A & #{imm}                          | 0 |   |   |   |   |   | 0 | 0 |

| ANC  |     | \$2B |      |      |      |      |      |      |      |      | A = A & #{imm}                          | 0 |   |   |   |   |   | 0 | 0 |

| ALR  |     | \$4B |      |      |      |      |      |      |      |      | A = (A & #{imm}) / 2                    | 0 |   |   |   |   |   | 0 | 0 |

| ARR  |     | \$6B |      |      |      |      |      |      |      |      | A = (A & #{imm}) / 2                    | 0 | 0 |   |   | i |   | 0 | х |

| SBX  |     | \$CB |      |      |      |      |      |      |      |      | X = A & X - #{imm}                      | 0 |   |   |   |   |   | 0 | 0 |

| SBC  |     | \$EB |      |      |      |      |      |      |      |      | A = A - #{imm}                          | 0 | 0 |   |   | i |   | 0 | х |

| SHA  |     |      |      |      |      |      | \$93 |      |      | \$9F | {addr} = A & X & {H+1}                  |   |   |   |   |   |   |   |   |

| SHY  |     |      |      |      |      |      |      |      | \$9C |      | {addr} = Y & {H+1}                      |   |   |   |   |   |   |   |   |

| SHX  |     |      |      |      |      |      |      |      |      | \$9E | {addr} = X & {H+1}                      |   |   |   |   |   |   |   |   |

| TAS  |     |      |      |      |      |      |      |      |      | \$9B | SP = A & X<br>{addr} = SP & {H+1}       |   |   |   |   |   |   |   |   |

| LAS  |     |      |      |      |      |      |      |      |      | \$BB | A,X,SP = {addr} & SP                    | 0 |   |   |   |   |   | 0 |   |

| LAX  |     | \$AB |      |      |      |      |      |      |      |      | A,X = (A   CONST) & #{imm}              | 0 |   |   |   |   |   | 0 |   |

| ANE  |     | \$8B |      |      |      |      |      |      |      |      | A = (A   CONST) & X & #{imm}            | 0 |   |   |   |   |   | 0 |   |

| Opc. | imp  | imm  | zp   | zpx  | zpy | izx | izy | abs  | abx  | aby | Function  | N | ٧ | - | В | D | Ι | Z | С |

|------|------|------|------|------|-----|-----|-----|------|------|-----|-----------|---|---|---|---|---|---|---|---|

| NOP  | \$1A | \$80 | \$04 | \$14 |     |     |     | \$0C | \$1C |     | No effect |   |   |   |   |   |   |   |   |

| NOP  | \$3A | \$82 | \$44 | \$34 |     |     |     |      | \$3C |     | No effect |   |   |   |   |   |   |   |   |

| NOP  | \$5A | \$C2 | \$64 | \$54 |     |     |     |      | \$5C |     | No effect |   |   |   |   |   |   |   |   |

| NOP  | \$7A | \$E2 |      | \$74 |     |     |     |      | \$7C |     | No effect |   |   |   |   |   |   |   |   |

| NOP  | \$DA | \$89 |      | \$D4 |     |     |     |      | \$DC |     | No effect |   |   |   |   |   |   |   |   |

| NOP  | \$FA |      |      | \$F4 |     |     |     |      | \$FC |     | No effect |   |   |   |   |   |   |   |   |

| Opc. | -    | -    | -    | -    | -    | -    | -    | -    | -    | -    | -    | -    | Function    | N | ٧ | - | В | D | Ι | Z | С |

|------|------|------|------|------|------|------|------|------|------|------|------|------|-------------|---|---|---|---|---|---|---|---|

| JAM  | \$02 | \$12 | \$22 | \$32 | \$42 | \$52 | \$62 | \$72 | \$92 | \$B2 | \$D2 | \$F2 | CPU lock-up |   |   |   |   |   |   |   |   |

Types

# Combinations of two operations with the same addressing mode

| 0pcode     | Function                                        |

|------------|-------------------------------------------------|

| SLO {addr} | ASL {addr} + ORA {addr}                         |

| RLA {addr} | ROL {addr} + AND {addr}                         |

| SRE {addr} | LSR {addr} + EOR {addr}                         |

| RRA {addr} | ROR {addr} + ADC {addr}                         |

| SAX {addr} | STA {addr} + STX {addr} store A & X into {addr} |

| LAX {addr} | LDA {addr} + LDX {addr}                         |

| DCP {addr} | DEC {addr} + CMP {addr}                         |

| ISC {addr} | INC {addr} + SBC {addr}                         |

# Combinations of an immediate and an implied command

| Opcode     | Function                                       |

|------------|------------------------------------------------|

| ANE #{imm} | TXA + AND #{imm}                               |

| LAX #{imm} | LDA #{imm} + TAX                               |

| ANC #{imm} | AND #{imm} + (ASL)                             |

| ANC #{imm} | AND #{imm} + (ROL)                             |

| ALR #{imm} | AND #{imm} + LSR                               |

| ARR #{imm} | AND #{imm} + ROR                               |

| SBX #{imm} | CMP #{imm} + DEX put A & X minus #{imm} into X |

| SBC #{imm} | SBC #{imm} + NOP                               |

# **Combinations of STA/STX/STY**

| 0   | pcode  | Function                     |

|-----|--------|------------------------------|

| SHA | {addr} | stores A & X & H into {addr} |

| SHX | {addr} | stores X & H into {addr}     |

| SHY | {addr} | stores Y & H into {addr}     |

# **Combinations of STA/TXS and LDA/TSX**

| 0pcode       | Function                                       |

|--------------|------------------------------------------------|

| TAS {addr} s | stores A & X into SP and A & X & H into {addr} |

| LAS {addr} s | stores {addr} & SP into A, X and SP            |

# No effect

Bit configuration does not allow any operation on these ones:

| Op  | ocode  | Function                           |

|-----|--------|------------------------------------|

| NOP |        | no effect                          |

| NOP | #{imm} | Fetches #{imm} but has no effects. |

| NOP | {addr} | Fetches {addr} but has no effects. |

# Lock-up

| 0pcode | Function                                     |

|--------|----------------------------------------------|

| JAM    | Halt the CPU. The buses will be set to \$FF. |

# Stable Opcodes

# SLO (ASO)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: ASL, ORA)

| Орс. | Mnemonic    | Function            | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|-------------|---------------------|------|--------|---|---|---|---|---|---|---|---|

| \$07 | SLO zp      | {addr} = {addr} * 2 | 2    | 5      | 0 |   |   |   |   |   | 0 | 0 |

| \$17 | SLO zp, x   |                     | 2    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$03 | SLO (zp, x) |                     | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$13 | SLO (zp), y |                     | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$0F | SLO abs     |                     | 3    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$1F | SLO abs, x  |                     | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

| \$1B | SLO abs, y  |                     | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

**Operation**: Shift left one bit in memory, then OR accumulator with memory.

- The leftmost bit is shifted into the carry flag

- N and Z are set after the ORA

#### Example:

SLO \$C010 ; 0F 10 C0

**Equivalent Instructions:**

ASL \$C010 ORA \$C010

**Test code**: Lorenz-2.15/asoa.prg, Lorenz-2.15/asoax.prg, Lorenz-2.15/asoay.prg, Lorenz-2.15/asoix.prg, Lorenz-2.15/asoiy.prg, Lorenz-2.15/asoz.prg, Lorenz-2.15/asozx.prg

# Example: Multibyte left shift and load leftmost byte

```

Instead of:

ASL data+2

ROL data+1

ROL data+0

LDA data+2

you can write: (which is shorter)

SLO data+2

ROL data+1

ROL data+1

ROL data+0

Compared by A is zero before reaching here

ROL data+1

ROL data+0

```

# **RLA (RLN)**

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: ROL, AND)

| Opc. | Mnemonic    | Function                             | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|-------------|--------------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$27 | RLA zp      | {addr} = rol {addr} A = A and {addr} | 2    | 5      | 0 |   |   |   |   |   | 0 | х |

| \$37 | RLA zp, x   |                                      | 2    | 6      | 0 |   |   |   |   |   | 0 | х |

| \$23 | RLA (zp, x) |                                      | 2    | 8      | 0 |   |   |   |   |   | 0 | х |

| \$33 | RLA (zp), y |                                      | 2    | 8      | 0 |   |   |   |   |   | 0 | х |

| \$2F | RLA abs     |                                      | 3    | 6      | 0 |   |   |   |   |   | 0 | х |

| \$3F | RLA abs, x  |                                      | 3    | 7      | 0 |   |   |   |   |   | 0 | x |

| \$3B | RLA abs, y  |                                      | 3    | 7      | 0 |   |   |   |   |   | 0 | X |

**Operation**: Rotate one bit left in memory, then AND accumulator with memory.

- Carry is shifted in as LSB and bit 7 is shifted into Carry

- N and Z are set according to the AND

#### Example:

RLA \$FC,X ;37 FC

**Equivalent Instructions:**

ROL \$FC,X AND \$FC,X

Test code: Lorenz-2.15/rlaa.prg, Lorenz-2.15/rlaax.prg, Lorenz-2.15/rlaay.prg, Lorenz-2.15/rlaix.prg, Lorenz-2.15/rlaiy.prg, Lorenz-2.15/rlazx.prg

#### Example: scroll over a background layer

STA buffer

Lets say you want to create a scroller that moves text over some fixed background graphics. Suppose the data of the sliding text is stored at Scrollgfx and the data of the fixed background at backgroundgfx. The actual data that is displayed is located at buffer.

Combining the sliding and fixed data without RLA would go something like (for the rightmost byte of the top line of the gfx data) this:

```

ROL scrollgfx ; shift left (with carry)

LDA scrollgfx

AND backgroundgfx ; combine with background

```

... which takes 18 cycles in 16 bytes

instead you can write:

```

LDA backgroundgfx

RLA scrollgfx ; shift left and combine with bg

STA buffer

```

... which takes 14 cycles in 12 bytes

#### Example: multiply by 3, 5, 7, 10 ...

Especially if you can make sure the carry flag will not get in the way, RLA can be used to perform a "multiply and accumulate" to build various non-power-of-two multiplications:

```

CLC

STA

zp

; A * 3

RLA

zp

; A * 7

RLA zp

; A * 15

RLA zp

CLC

STA

zp

RLA zp

; A * 3

ADC zp

; A * 5

: A * 10

ROL

```

# SRE (LSE)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: LSR, EOR)

| Opc. | Mnemonic    | Function                             | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|-------------|--------------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$47 | SRE zp      | {addr} = {addr} / 2 A = A eor {addr} | 2    | 5      | 0 |   |   |   |   |   | 0 | 0 |

| \$57 | SRE zp, x   |                                      | 2    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$43 | SRE (zp, x) |                                      | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$53 | SRE (zp), y |                                      | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$4F | SRE abs     |                                      | 3    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$5F | SRE abs, x  |                                      | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

| \$5B | SRE abs, y  |                                      | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

**Operation**: Shift right one bit in memory, then EOR accumulator with memory.

- LSB is shifted into the carry flag

- N and Z are set after the EOR

#### Example:

SRE \$C100,X ;5F 00 C1

**Equivalent Instructions:**

LSR \$C100,X EOR \$C100,X

Test code: Lorenz-2.15/lsea.prg, Lorenz-2.15/lseax.prg,

Lorenz-2.15/lseay.prg, Lorenz-2.15/lseix.prg,

Lorenz-2.15/lseiy.prg, Lorenz-2.15/lsez.prg, Lorenz-2.15/lsezx.prg

#### Example: 8bit 1-of-8 counter

SRE shifts the content of a memory location to the right and EORs the content with A, while SLO shifts to the left and does an OR instead of EOR.

So this is nice to combine the previous described 8 bit counter with for e.g. setting pixels:

```

LDA #$80

STA pix

LDA (zp),y

SRE pix

;shift mask one to the right

;and eor mask with A

BCS advance column

;did the counter under-run?

;so advance column

STA (zp), y

advance column:

ROR pix

;reset counter

ORA #$80

;set first pixel

STA (zp), y

LDA zp

;advance column

;CLC

;is still clear

ADC #$08

STA zp

BCC +

INC zp+1

```

# RRA (RRD)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: ROR, ADC)

| Opc. | Mnemonic    | Function                             | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|-------------|--------------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$67 | RRA zp      | {addr} = ror {addr} A = A adc {addr} | 2    | 5      | 0 | 0 |   |   | i |   | 0 | х |

| \$77 | RRA zp, x   |                                      | 2    | 6      | 0 | 0 |   |   | i |   | 0 | х |

| \$63 | RRA (zp, x) |                                      | 2    | 8      | 0 | 0 |   |   | i |   | 0 | х |

| \$73 | RRA (zp), y |                                      | 2    | 8      | 0 | 0 |   |   | i |   | 0 | х |

| \$6F | RRA abs     |                                      | 3    | 6      | 0 | 0 |   |   | i |   | 0 | х |

| \$7F | RRA abs, x  |                                      | 3    | 7      | 0 | 0 |   |   | i |   | 0 | х |

| \$7B | RRA abs, y  |                                      | 3    | 7      | 0 | 0 |   |   | i |   | 0 | х |

**Operation**: Rotate one bit right in memory, then add memory to accumulator (with carry).

- Bit 1 is shifted out into the carry flag and Carry flag is shifted into bit 7 by the ROR

- then all flags are set according to the ADC

This instruction inherits the decimal flag dependency from ADC. For the behaviour in decimal mode see Unintended decimal mode: RRA (RRD).

```

Example:

RRA $030C ; 6F 0C 03

Equivalent Instructions:

ROR $030C

ADC $030C

```

```

Test code: Lorenz-2.15/rraa.prg, Lorenz-2.15/rraax.prg, Lorenz-2.15/rraay.prg, Lorenz-2.15/rraix.prg, Lorenz-2.15/rraiy.prg, Lorenz-2.15/rraz.prg, Lorenz-2.15/rrazx.prg, 64doc/droradc.prg

```

# Example: noise LFSR

```

If you need a fast "noise" generator, something like this could work:

LDA #$e4; initial seed

STA zp1

LDA #$01; initial seed

CLC

...

; restore accu and carry

RRA zp1

EOR #$01

ROR

; "noise" value in accu

; preserve accu and carry

...

```

# SAX (AXS, AAX)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: STA, STX)

| Opc. | Mnemonic    | Function       | Size | Cycles | N | ٧ | - | В | D | I | z | С |

|------|-------------|----------------|------|--------|---|---|---|---|---|---|---|---|

| \$87 | SAX zp      | {addr} = A & X | 2    | 3      |   |   |   |   |   |   |   |   |

| \$97 | SAX zp, y   |                | 2    | 4      |   |   |   |   |   |   |   |   |

| \$83 | SAX (zp, x) |                | 2    | 6      |   |   |   |   |   |   |   |   |

| \$8F | SAX abs     |                | 3    | 4      |   |   |   |   |   |   |   |   |

**Operation**: AND the contents of the A and X registers (without changing the contents of either register) and stores the result in memory.

| Example:                           |                                 |

|------------------------------------|---------------------------------|

| SAX \$FE                           | ;87 FE                          |

| Equivalent Instructions:           |                                 |

| PHP<br>PHA<br>STX \$FE             | ; save flags and accumulator    |

| AND \$FE<br>STA \$FE<br>PLA<br>PLP | ; restore flags and accumulator |

Note that SAX does not affect any flags in the processor status register, and does not modify A/X. It would also not actually use the stack, which is only needed to mimic the behaviour with legal opcodes in this example.

```

Test code: Lorenz-2.15/axsa.prg, Lorenz-2.15/axsix.prg, Lorenz-2.15/axsz.prg, Lorenz-2.15/axszy.prg

```

Note that two addressing modes that SAX is missing, absolute Y indexed and indirect Y indexed, can be simulated by using the SHA instruction, see SHA (AXA, AHX, TEA).

'The SAX instruction decodes to two instructions (STA and STX) whose behaviour is identical except that one hits the output-enable signal for the accumulator, and the other hits the output-enable signal for the X register. Although it would seem that this would cause ambiguous behaviour, it turns out that during one half of each cycle the internal operand-output bus is set to all '1's, and the read-enable signals for the accumulator and X register (and Y register, stack pointer, etc.) only allow those registers to set the internal operand-output bus bits to '0'. Thus, if a bit is zero in either the accumulator or the X register, it will be stored as zero; if it's set to '1' in both, then nothing will pull down the bus so it will output '1'.'

#### Example: store values with mask

This opcode is ideal to set up a permanent mask and store values combined with that mask:

LDX #\$aa ;set up mask

LDA \$1000,y ;load A

SAX \$80,y ;store A & \$aa

## Example: update Sprite Pointers

Often you need to set up all 8 sprite pointers in as few cycles as possible, this could be done like this:

LDA #\$01

LDX #\$fe

SAX screen + \$3f8 ;00

STA screen + \$3f9 ;01

LDA #\$03

SAX screen + \$3fa ;02

STA screen + \$3fb ;03

LDA #\$05

SAX screen + \$3fc ;04

STA screen + \$3fd ;05

LDA #\$07

SAX screen + \$3fe ;06

STA screen + \$3ff ;07

LAX

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: LDA, LDX)

| Opc. | Mnemonic    | Function     | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|-------------|--------------|------|--------|---|---|---|---|---|---|---|---|

| \$A7 | LAX zp      | A,X = {addr} | 2    | 3      | 0 |   |   |   |   |   | 0 |   |

| \$B7 | LAX zp, y   |              | 2    | 4      | 0 |   |   |   |   |   | 0 |   |

| \$A3 | LAX (zp, x) |              | 2    | 6      | 0 |   |   |   |   |   | 0 |   |

| \$B3 | LAX (zp), y |              | 2    | 5 (+1) | 0 |   |   |   |   |   | 0 |   |

| \$AF | LAX abs     |              | 3    | 4      | 0 |   |   |   |   |   | 0 |   |

| \$BF | LAX abs, y  |              | 3    | 4 (+1) | 0 |   |   |   |   |   | 0 |   |

**Operation**: Load both the accumulator and the X register with the contents of a memory location.

Example:

LAX \$8400,Y ;BF 00 84

**Equivalent Instructions:**

LDA \$8400,Y TAX

Test code: Lorenz-2.15/laxa.prg, Lorenz-2.15/laxay.prg, Lorenz-2.15/laxix.prg, Lorenz-2.15/laxiy.prg, Lorenz-2.15/laxzy.prg

#### Example: load A and X with same value

Loading A and X with the same value is ideal if you manipulate the original value, but later on need the value again. Instead of loading it again you can either transfer it again from the other register, or combine A and X again with another illegal opcode.

```

LAX $1000,y ;load A and X with value from $1000,y

```

EOR #\$80 ;manipulate A

STA (\$fd),y ;store A LDA #\$f8 ;load mask SAX jump+1 ;store A & X

Also one could so:

```

LAX $1000,y ;load A and X with value from $1000,y

```

EOR #\$80 ;manipulate A

STA (\$fd),y ;store A

TXA ; fetch value again

EOR #\$40 ;manipulate

STA (\$fb),y ;store

# DCP (DCM)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: DEC, CMP)

| Opc. | Mnemonic    | Function                         | Size | Cycles | N | V | - | В | D | Ι | Z | С |

|------|-------------|----------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$C7 | DCP zp      | {addr} = {addr} - 1 A cmp {addr} | 2    | 5      | 0 |   |   |   |   |   | 0 | 0 |

| \$D7 | DCP zp, x   |                                  | 2    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$C3 | DCP (zp, x) |                                  | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$D3 | DCP (zp), y |                                  | 2    | 8      | 0 |   |   |   |   |   | 0 | 0 |

| \$CF | DCP abs     |                                  | 3    | 6      | 0 |   |   |   |   |   | 0 | 0 |

| \$DF | DCP abs, x  |                                  | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

| \$DB | DCP abs, y  |                                  | 3    | 7      | 0 |   |   |   |   |   | 0 | 0 |

**Operation**: Decrement the contents of a memory location and then compare the result with the A register.

• N/Z/C are set according to the compare, after the decrement

```

Example:

DCP $FF ; C7 FF

Equivalent Instructions:

DEC $FF

CMP $FF

```

```

Test code: Lorenz-2.15/dcma.prg, Lorenz-2.15/dcmax.prg, Lorenz-2.15/dcmay.prg, Lorenz-2.15/dcmix.prg, Lorenz-2.15/dcmiy.prg, Lorenz-2.15/dcmz.prg, Lorenz-2.15/dcmzx.prg, 64doc/dincsbc-deccmp.prg

```

## Example: decrementing loop counter

## Example: decrementing 16bit counter

```

For decrementing a 16 bit pointer it is also of good use:

LDA #$ff

DCP ptr

BNE +

DEC ptr+1

+

; carry is set always for free

```

## ISC (ISB, INS)

**Type**: Combination of two operations with the same addressing mode (Sub-instructions: INC, SBC)

| Opc. | Mnemonic    | Function                                    | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|-------------|---------------------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$E7 | ISC zp      | $\{addr\} = \{addr\} + 1  A = A - \{addr\}$ | 2    | 5      | 0 | 0 |   |   | i |   | 0 | х |

| \$F7 | ISC zp, x   |                                             | 2    | 6      | 0 | 0 |   |   | i |   | 0 | х |

| \$E3 | ISC (zp, x) |                                             | 2    | 8      | 0 | 0 |   |   | i |   | 0 | х |

| \$F3 | ISC (zp), y |                                             | 2    | 8      | 0 | 0 |   |   | i |   | 0 | х |

| \$EF | ISC abs     |                                             | 3    | 6      | 0 | 0 |   |   | i |   | 0 | х |

| \$FF | ISC abs, x  |                                             | 3    | 7      | 0 | 0 |   |   | i |   | 0 | х |

| \$FB | ISC abs, y  |                                             | 3    | 7      | 0 | 0 |   |   | i |   | 0 | х |

**Operation**: Increase memory by one, then subtract memory from accumulator (with borrow).

• C is affecting the SBC, and SBC sets N / V / Z / C as expected

This instruction inherits the decimal flag dependency from SBC. For the behaviour in decimal mode see Unintended decimal mode: ISC (ISB, INS).

```

Example:

ISC $FF ; E7 FF

Equivalent Instructions:

INC $FF

SBC $FF

```

```

Test code: Lorenz-2.15/insa.prg, Lorenz-2.15/insax.prg, Lorenz-2.15/insay.prg, Lorenz-2.15/insix.prg, Lorenz-2.15/insiy.prg, Lorenz-2.15/insz.prg, Lorenz-2.15/inszx.prg, 64doc/dincsbc.prg

```

#### Example: incrementing loop counter

```

Instead of:

INC counter

LDA counter

CMP #ENDVALUE

BNE next

you can write: (which saves a cycle when counter is in zero-page)

LDA #ENDVALUE

SEC

ISC counter

BNE next

```

# Example: increment indexed and load value

```

Instead of:

; A is zero and C=0 before reaching here INC buffer, x LDA buffer, x

you can write: (which saves a byte if buffer is in regular memory, and is faster)

; A is zero and C=0 before reaching here ISC buffer, x EOR #$ff

```

# **ANC (ANC2, ANA, ANB)**

Type: Combination of an immediate and an implied command (Sub-instructions: AND, ASL/ROL)

| Opc. | Mnemonic | Function       | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|----------|----------------|------|--------|---|---|---|---|---|---|---|---|

| \$0B | ANC #imm | A = A & #{imm} | 2    | 2      | 0 |   |   |   |   |   | 0 | 0 |

| \$2B | ANC #imm | A = A & #{imm} | 2    | 2      | 0 |   |   |   |   |   | 0 | 0 |

**Operation**: ANDs the contents of the A register with an immediate value and then moves bit 7 of A into the Carry flag.

• This opcode works basically identically to AND #imm. except that the Carry flag is set to the same state that the Negative flag is set to. (bit 7 is put into the carry, as if the ASL/ROL would have been executed)

Example:

ANC #\$AA ;2B AA

Equivalent Instructions:

AND #\$AA

; ROL A - not actually executed, set C as if it was

Test code: Lorenz-2.15/ancb.prg

#### Example: implicit enforcement of carry flag state

When using an AND instruction before an addition (or any other operation where you might want to know the state of the carry flag), you might save two cycles (not having to do CLC or SEC) by using ANC instead of AND. Since a cleared high bit in the value used with the ANC instruction always leads to a unset carry flag after this operation, you can take advantage of that. An example:

LDA value

ANC #\$0f ;Carry flag is always set to 0

;after this op.

ADC value2 ; Add a value. CLC not needed!

STA result

Another case like this is when you want to set the A register to #\$00 specifically, and also happen to want to have the carry cleared:

ANC #0 ;Carry always cleared after this op,

; and A register always set to zero.

#### Example: remembering a bit

You can use ANC to simply putting the highest bit of a byte into the carry flag without affecting a register (by using ANC #\$FF). This can be useful sometimes since not that many instructions destroy the (C)arry flag as well as the (N)egative flag (mainly mathematical operations, shifting operations and comparison operations), in order to 'remember' this information during the execution of other code (such as some LDA/STA stuff).

A command that does this too is CMP #\$80 (as well as CPX and CPY), which non destructively puts the high bit of a register into Carry as well.

# ALR (ASR)

**Type**: Combination of an immediate and an implied command (Sub-instructions: AND, LSR)

| Opc. | Mnemonic | Function             | Size | Cycles | N | ٧ | В | D | I | Z | С |

|------|----------|----------------------|------|--------|---|---|---|---|---|---|---|

| \$4B | ALR #imm | A = (A & #{imm}) / 2 | 2    | 2      | 0 |   |   |   |   | 0 | 0 |

**Operation**: AND the contents of the A register with an immediate value and then LSRs the result.

- Bit 1 (after the AND) is shifted into the carry flag

- N and Z are set after the shift

Example:

ALR #\$FE ;4B FE

**Equivalent Instructions:**

AND #\$FE LSR A

Test code: Lorenz-2.15/alrb.prg

# Example: right shift and mask

Whenever you need to shift and influence the carry afterwards, you can use ALR for that, and if you even need to apply an and-mask beforehand, you are extra lucky and can do 3 commands by that:

ALR #fe ;-> A & fe = fe -> lsr -> carry is cleared

; as bit 0 was not set before lsr

... same as ...

AND #\$ff

LSR

CLC

#### Example: fetch 2 bits from a byte

```

LDA #%10110110

LSR

ALR #$03*2

```

This will mask out and shift down bits 2 and 3. Note that the mask is applied before shifting, therefore the mask is multiplied by two.

#### Example: add offset depending on LSB

Another nice trick to transform a single bit into a new value (good for adding offsets depending on the value of a single bit) offset is the following:

LDA xposl ;load a value

ALR #\$01 ;move LSB to carry and clear A

BCC +

LDA #\$3f ;carry is set

+

ADC #stuff ;things will work sane, as offset

; includes already the carry

As you can see we have now either loaded \$00 or \$40 (carry!) to A depending on the state of bit 0, that is ideal for e.g. when we want to load from a different bank depending on if a position is odd or even. As you see, the above example is even faster than this (as the shifting always takes 6 cycles, whereas the above example takes 5/6 cycles):

LDA xposl

ALR #\$01

ROR LSR

ADC #stuff ;things will work sane as carry is

;always clear (upper bits are masked)

#### **ARR**

**Type**: Combination of an immediate and an implied command (Sub-instructions: AND, ROR)

| Opc. | Mnemonic | Function             | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|----------|----------------------|------|--------|---|---|---|---|---|---|---|---|

| \$6B | ARR #imm | A = (A & #{imm}) / 2 | 2    | 2      | 0 | 0 |   |   | i |   | 0 | х |

note to ARR: part of this command are some ADC mechanisms. following effects appear after AND but before ROR: the V-Flag is set according to (A and #{imm}) + #{imm}, bit 0 does NOT go into carry, but bit 7 is exchanged with the carry.

The following applies to when the decimal flag is clear, for the behaviour in decimal mode see Unintended decimal mode: ARR.

ARR ANDs the accumulator with an immediate value and then rotates the content right. The resulting carry is however not influenced by the LSB as expected from a normal rotate. The Carry and the state of the overflow-flag depend on the state of bit 6 and 7 before the rotate occurs, but after the and-operation has happened, and will be set like shown in the following table:

| Inpu  | Input before ROR Output |       |               |                             |               |               |  |  |  |

|-------|-------------------------|-------|---------------|-----------------------------|---------------|---------------|--|--|--|

| Carry | Bit 7                   | Bit 6 | Carry         | Overflow                    | Bit 7         | Bit 6         |  |  |  |

|       |                         |       | = Input Bit 7 | = Input Bit 7 ^ Input Bit 6 | = Input Carry | = Input Bit 7 |  |  |  |

| 0     | 0                       | 0     | 0             | 0                           | 0             | 0             |  |  |  |

| 0     | 0                       | 1     | 0             | 1                           | 0             | 0             |  |  |  |

| 0     | 1                       | 0     | 1             | 1                           | 0             | 1             |  |  |  |

| Θ     | 1                       | 1     | 1             | 0                           | 0             | 1             |  |  |  |

| 1     | 0                       | 0     | 0             | 0                           | 1             | 0             |  |  |  |

| 1     | 0                       | 1     | 0             | 1                           | 1             | 0             |  |  |  |

| 1     | 1                       | 0     | 1             | 1                           | 1             | 1             |  |  |  |

| 1     | 1                       | 1     | 1             | 0                           | 1             | 1             |  |  |  |

Example:

ARR #\$7F ;6B 7F

**Equivalent Instructions:**

AND #\$7F

ROR A ; flags are different with ARR, see the

; above table

Test code: CPU/asap/cpu decimal.prg, Lorenz-2.15/arrb.prg

## Example: rotating 16 bit values

```

LDA #>addr

LSR

STA $fc

ARR #$00 ; A = A & $00 -> ror A

STA $fb

... is the same as ...

LDA #>addr

LSR

STA $fc

LDA #$00

ROR

STA $fb

```

Note: Again, you can influence the final state of the carry by either using #\$00 or #\$01 for the LDA (\$00 or \$80 in case of ARR, but the later only if A has bit 7 set as well, so be carefully here).

#### Example: load register depending on carry

If you need to load a register depending on some branch, you might be able to save some cycles. Imagine you have the following to load Y depending on the state of the carry:

```

CMP $1000

BCS +

LDY #$00

BEQ ++ ; jump always

+

LDY #$80

++

This can be solved in less cycles and less memory:

CMP $1000

ARR #$00

TAY

```

## Example: shift zeros or ones into accumulator

Due to the fact that the carry resembles the state of bit 7 after ARR is executed, one can continuously shift in zeroes or ones into a byte:

```

LDA #$80

SEC

ARR #$ff

; -> A = $c0 -> sec

ARR #$ff

; -> A = \$e0 -> sec

ARR #$ff

; -> A = $f0 -> sec

LDA #$7f

CLC

ARR #$ff

; -> A = \$3f -> clc

ARR #$ff

; -> A = $1f -> clc

: -> A = \$0f -> clc

ARR #$ff

```

## SBX (AXS, SAX, XMA)

**Type**: Combination of an immediate and an implied command (Sub-instructions: CMP, DEX)

| Opc. | Mnemonic | Function           | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|----------|--------------------|------|--------|---|---|---|---|---|---|---|---|

| \$CB | SBX #imm | X = A & X - #{imm} | 2    | 2      | 0 |   |   |   |   |   | 0 | 0 |

**Operation**: SBX ANDs the contents of the A and X registers (leaving the contents of A intact), subtracts an immediate value, and then stores the result in X. ... A few points might be made about the action of subtracting an immediate value. It actually works just like the CMP instruction, except that CMP does not store the result of the subtraction it performs in any register.

- This subtract operation is not affected by the state of the Carry flag, though it does affect the Carry flag. It does not affect the Overflow flag. (Flags are set like with CMP, not SBC)

- N and Z are set according to the value ending up in X

Another property of this opcode is that it doesn't respect the decimal mode, since it is derived from CMP rather than SBC. So if you need to perform table lookups and arithmetic in a tight interrupt routine there's no need to clear the decimal flag in case you've got some code running that operates in decimal mode.

```

Example:

```

SBX #\$5A ;CB 5A

Equivalent Instructions:

STA \$02 ; save accumulator

TXA ; hack because there is no 'AND WITH X'

AND \$02 ; instruction

CMP #\$5A ; set flags like CMP

PHP ; save flags

SEC

CLD ; subtract without being affected by

SBC #\$5A ; decimal mode

TAX

LDA \$02 ; restore accumulator

PLP ; restore flags

Note: SBX is not easily expressed entirely correct using legal opcodes. Memory location \$02 would not be altered by the SBX opcode, and it would not use the stack.

**Test code**: Lorenz-2.15/sbxb.prg, 64doc/sbx.prg, 64doc/vsbx.prg, 64doc/sbx-c100.prg

## Example: decrement X by more than 1

Sometimes you need/want to decrease the X register by more than one. That is often done by the following piece of code:

```

TXA

SEC

SBC #$xx ;where xx is (obviously) the value

;to decrease by

TAX

```

This procedure takes 8 cycles (and 5 bytes in memory). If the value of the carry flag is always known at this point in the code, it can be removed and the snippet would then take 6 cycles (and 4 bytes in memory). However, you can use SBX like this:

And the modified code snippet using SBX instead looks like this:

```

LDA #$ff ; Next opcode contains a implicit AND with ; the A register, so turn all bits ON!

SBX #$xx ; where xx is the value to decrease by

```

This code kills the A register of course, but so does the 'standard' version above. It can be made even shorter by using a 'txa' instruction instead of the 'lda #\$ff'. That works since X and A will be equal after the 'txa', and ANDing a value with itself produces no change, hence the AND effect of SBX is 'disarmed' and the subtraction will proceed as expected:

```

TXA

SBX #$xx

```

Note that in this case you do not have to worry about the carry flag at all, and all in all the whole procedure takes only 4 cycles (and 3 bytes in memory)

### Example: decrement nibbles

Imagine you have a byte that is divided into two nibbles (just what you often use in  $4\times4$  effects), now you want to decrement each nibble, but when the low nibble underflows, this will decrement the high nibble as well, here the SBX command can help to find out about that special case:

```

LDA $0400, y

;load value

LDX #$0f

;set up mask

SBX #$00

;check if low nibble underflows

: -> X = A \& \$0f

BNE +

;all fine, decrement both nibbles

;the cheap way, carry is set!

SBC #$f0

; do wrap around by hand

SEC

SBC #$11

;decrement both nibbles,

; carry is set already by sbx

... can be substituted by ...

LDA #$0f

;set up mask beforehand,

:can be reused for each turn

STA $02

LDA $0400, y

BIT $02

;apply mask without destroying A

BNE +

CLC

ADC #$10

+

SEC

;we need to set carry

SBC #$11

```

## Example: apply a mask to an index

Furthermore, the SBX command can also be used to apply a mask to an index easily:

LDX #\$03 ; mask

LDA val1 ;load value

SBX #\$00 ;mask out lower 2 bits -> X

LSR ; A is untouched, so we can continue

;doing stuff with A

LSR

STA val1

LDA colours,x ;fetch colour from table

instead of (which takes 3 cycles more):

LDA val1

AND #\$03

TAX ;set up index

LSR val1 ;A is clobbered, so shift direct

LSR val1

LDA colours,x

The described case makes it easy to decode 4 multicolour pixel pairs by always setting up an index from the lowest two bits and fetching the appropriate colour from a previously set up table.

# SBC (USBC, USB)

**Type**: Combination of an immediate and an implied command (Sub-instructions: SBC, NOP)

| Opc. | Mnemonic | Function       | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|----------|----------------|------|--------|---|---|---|---|---|---|---|---|

| \$EB | SBC #imm | A = A - #{imm} | 2    | 2      | 0 | 0 |   |   | i |   | 0 | х |

**Operation**: subtract immediate value from accumulator with carry. Same as the regular SBC.

Test code: Lorenz-2.15/sbcb-eb.prg

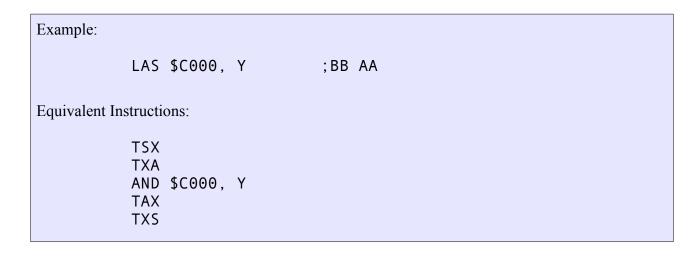

## LAS (LAR)

**Type**: Combinations of STA/TXS and LDA/TSX

| Opc. | Mnemonic   | Function             | Size | Cycles | N | ٧ | - | В | D | Ι | z | С |

|------|------------|----------------------|------|--------|---|---|---|---|---|---|---|---|

| \$BB | LAS abs, y | A,X,SP = {addr} & SP | 3    | 4 (+1) | 0 |   |   |   |   |   | 0 |   |

**Operation**: AND memory with stack pointer, transfer result to accumulator, X register and stack pointer.

• N and Z are set as expected by a load instruction

Test code: CPU/asap/cpu\_las.prg, Lorenz-2.15/lasay.prg

Note: LAS is called as 'probably unreliable' in one source - this does not seem to be the case though

It can be the case that the stack is not used in a main routine, since it is cheaper to store things in the zeropage. Of course when a subroutine is called or an interrupt triggers the return address (and status register in case of an IRQ) is stored on the stack, but after returning to the main loop the stackpointer (SP) is back to the same value again. This means that you can change the SP at will in the main loop without messing things up. For example, you can use it as temporary storage of the X register with TXS/TSX. This makes it possible to use LAS (and TAS).

### Example: cycle an index within bounds

If you want to cycle an index and wrap around to zero at a number that is a power of two, you could do that with LAS. For example to cycle from 0-15, suppose we start with SP=\$f7 (any value will work):

LAS mask,y; if Mask is one page filled with \$0f,

; this brings the SP to \$07 (and A and X

; as well) for any Y.

DEX ; X = \$06

TXS ; SP is now \$06, so the next time

; 'lda List,x' will pick the next value

LDA table, x ; use X as index

SP and X after the LAS instruction will always remain in the range 0-\$0f, no need to check for that!

Instead of the lda Table,x one could use pla if the data is on the stack and no interrupt can take place during this code snippet. Then dex should be replaced by e.g. sbx #\$11 to bring the SP to a safe area, to ensure the data on the stack is not messed up in other parts of the code.

# NOP (NPO, UNP)

Type: no effect

| Opc. | Mnemonic | Function     | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|----------|--------------|------|--------|---|---|---|---|---|---|---|---|

| \$1A | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

| \$3A | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

| \$5A | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

| \$7A | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

| \$DA | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

| \$FA | NOP      | No operation | 1    | 2      |   |   |   |   |   |   |   |   |

# NOP (DOP, SKB)

Type: no effect

| Opc. | Mnemonic | Function   | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|----------|------------|------|--------|---|---|---|---|---|---|---|---|

| \$80 | NOP #imm | Fetch #imm | 2    | 2      |   |   |   |   |   |   |   |   |

| \$82 | NOP #imm | Fetch #imm | 2    | 2      |   |   |   |   |   |   |   |   |

| \$C2 | NOP #imm | Fetch #imm | 2    | 2      |   |   |   |   |   |   |   |   |

| \$E2 | NOP #imm | Fetch #imm | 2    | 2      |   |   |   |   |   |   |   |   |

| \$89 | NOP #imm | Fetch #imm | 2    | 2      |   |   |   |   |   |   |   |   |

| Opc. | Mnemonic | Function     | Size | Cycles | N | ٧ | - | В | D | Ι | Z | С |

|------|----------|--------------|------|--------|---|---|---|---|---|---|---|---|

| \$04 | NOP zp   | Fetch {addr} | 2    | 3      |   |   |   |   |   |   |   |   |

| \$44 | NOP zp   | Fetch {addr} | 2    | 3      |   |   |   |   |   |   |   |   |

| \$64 | NOP zp   | Fetch {addr} | 2    | 3      |   |   |   |   |   |   |   |   |

| Opc. | Mnemonic  | Function     | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|-----------|--------------|------|--------|---|---|---|---|---|---|---|---|

| \$14 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

| \$34 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

| \$54 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

| \$74 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

| \$D4 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

| \$F4 | NOP zp, x | Fetch {addr} | 2    | 4      |   |   |   |   |   |   |   |   |

**Operation**: NOP zp and NOP zp, x actually perform a read operation. It's just that the value read is not stored in any register.

Note: NOP opcodes \$82, \$C2, \$E2 may be JAMs. Since only one source claims this, and no other sources corroborate this, it must be true on very few machines. On all others, these opcodes always perform 'no operation'. It is perhaps a good idea to avoid using them anyway.

Function

## NOP (TOP, SKW)

Mnemonic

Type: no effect

Opc.

| opc. | I III CIII OII I C | runceron     | 3120 | cycles | " | • |   |   |   | 1 | - | _ |

|------|--------------------|--------------|------|--------|---|---|---|---|---|---|---|---|

| \$0C | NOP abs            | Fetch {addr} | 3    | 4      |   |   |   |   |   |   |   |   |

| Орс. | Mnemonic           | Function     | Size | Cycles | N | ٧ | - | В | D | I | z | С |

| \$1C | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

| \$3C | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

| \$5C | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

| \$7C | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

| \$DC | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

| \$FC | NOP abs, x         | Fetch {addr} | 3    | 4 (+1) |   |   |   |   |   |   |   |   |

Size Cvcles N V - B D I Z C

**Operation**: These actually perform a read operation. It's just that the value read is not stored in any register. Further, opcode \$0C uses the absolute addressing mode. The two bytes which follow it form the absolute address. All the other 3 byte NOP opcodes use the absolute indexed X addressing mode. If a page boundary is crossed, the execution time of one of these NOP opcodes is upped to 5 clock cycles.

**Test code**: Lorenz-2.15/nopa.prg, Lorenz-2.15/nopax.prg, Lorenz-2.15/nopb.prg, Lorenz-2.15/nopn.prg, Lorenz-2.15/nopz.prg, Lorenz-2.15/nopzx.prg

## Example: acknowledge IRQ

If for some reason you want to acknowledge a timer IRQ and can not afford changing a register or the CPU status, you can use the fact that some of these NOPs actually perform a read operation:

NOP \$DCOD ; OC OD DC

## JAM (KIL, HLT, CIM, CRP)

Type: lock-up

| Opc. | Mnemonic | Function    | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|----------|-------------|------|--------|---|---|---|---|---|---|---|---|

| \$02 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$12 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$22 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$32 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$42 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$52 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$62 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$72 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$92 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$B2 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$D2 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

| \$F2 | JAM      | CPU lock-up | 1    | -      |   |   |   |   |   |   |   |   |

**Operation**: When one of these opcodes is executed, the byte following the opcode will be fetched, data- and address bus will be set to \$ff (all 1s) and program execution ceases. No hardware interrupts will execute either. Only a reset will restart execution. This opcode leaves no trace of any operation performed! No registers or flags affected.

Test code: CPU/cpujam/cpujamXX.prg

### Example: stop execution

Sometimes in a very memory constrained situation (like a 4k demo), you may want to stop execution of whatever is running with least effort – this can be achieved by using one of the JAM opcodes. Keep in mind though that only the CPU will stop.

LDA #0

STA \$D418

JAM ;02

#### **Simulation link:**

http://visual6502.org/JSSim/expert.html?graphics=f&a=0&steps=12&d=027fff00&loglevel=4

## **Unstable Opcodes**

Out of all opcodes, just seven fall into the so called 'unstable' category. This is where in earlier documents often the half esoteric black magic started, and what took most time and effort to update and fix for the current state of this version of the truth: Only two of those seven opcodes are actually unstable in the sense that they may produce a truly unpredictable result. The other five opcodes actually produce predictable results – but the conditions under which they do that and the produced results are a bit unexpected. All seven opcodes can be used safely when certain preconditions are met.

## 'unstable address high byte' group

There are five opcodes in this group. None of these opcodes affect the accumulator, the X register, the Y register, or the processor status register. They have two 'instabilities' which have to be 'disarmed' by careful programming.

- If the target address crosses a page boundary because of indexing, the instruction may not store at the intended address. Instead the high byte of the target address will get incremented as expected, and then ANDed with the value stored. For this reason you should generally keep your index in a range that page boundaries are not crossed.

- Sometimes the actual value is stored in memory and the AND with <addrhi+1> part drops off (ex. SHY becomes true STY). This happens when the RDY line is used to stop the CPU (pulled low), i.e. either a 'bad line' or sprite DMA starts in the second last cycle of the instruction. 'For example, it never seems to occur if either the screen is blanked or C128 2MHz mode is enabled.' For this reason you will have to choose a suitable target address based on what kind of values you want to store. 'For \$fe00 there's no problem, since anding with \$ff is the same as not anding. And if your values don't mind whether they are anded, e.g. if they are all \$00-\$7f for shy \$7e00,x, there is also no difference whether the and works or not.' If you make sure no DMA starts when any of these opcodes executes, the value written is always ANDed with the highbyte of the target address, plus one.

|         | SHA (zp), y | TAS abs, y | SHY abs, x | SHX abs, y | SHA abs,y |

|---------|-------------|------------|------------|------------|-----------|

| Opcode  | \$93        | \$9b       | \$9c       | \$9e       | \$9f      |

| Value   | A & X       | A & X      | Υ          | Х          | A & X     |

| Cycle N | 5           | 4          | 4          | 4          | 4         |

|                  | Highbyte of add   | lress written to | Value             | written        |

|------------------|-------------------|------------------|-------------------|----------------|

|                  | No DMA in Cycle N | DMA in Cycle N   | No DMA in Cycle N | DMA in Cycle N |

| Page not crossed | {H}               | {H}              | Value & {H+1}     | Value          |

| Page crossed     | {H+1} & Value     | {H+1} & Value    | Value & {H+1}     | Value          |

'To explain what's going on take a look at LDA ABX and STA ABX first.

LDA ABX takes 4 cycles unless a page wrap occurred (address+X lies in another page than address) in which case the value read during the 4th cycle (which was read with the original high byte) is discarded and in the 5th cycle a read is made again, this time from the correct address. During the 4th cycle the high address byte is incremented in order to have a correct high byte if the 5th cycle is necessary. The byte read from memory is buffered and copied to A during the read of the next command's opcode.

But there's a problem with storage commands: they need to put the value to write on the internal bus which is used for address computations as well. To avoid collisions STA ABX contains a fix-up which makes it always take 5 cycles (the value is always written in the 5th cycle as the high byte is computed in the 4th cycle).

This fix-up requires some transistors on the CPU; the guys at MOS forgot (or were unable?) to make them detect STX ABY (which becomes SHX) and a few others, they are missing that fix-up so this results in a collision between the value and high address byte computation.'

## SHA (AXA, AHX, TEA)

Type: Combinations of STA/STX/STY

| Opc. | Mnemonic    | Function               | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|-------------|------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$93 | SHA (zp), y | {addr} = A & X & {H+1} | 2    | 6      |   |   |   |   |   |   |   |   |

| \$9F | SHA abs, y  | {addr} = A & X & {H+1} | 3    | 5      |   |   |   |   |   |   |   |   |

**Operation**: This opcode stores the result of A AND X AND the high byte of the target address of the operand +1 in memory.

#### **Instabilities**:

- The value written is ANDed with &{H+1}, except when the RDY line goes low in the 4<sup>th</sup> (opcode \$9f) or 5<sup>th</sup> (opcode \$93) cycle.

- When adding Y to the target address causes a page boundary crossing, the highbyte of the target address is incremented by one (as expected), and then ANDed with (A & X).

```

Example:

SHA $7133.Y

:9F 33 71

Equivalent Instructions:

PHP

; save flags and accumulator

PHA

; hack which is needed because there is

STX $02

AND $02

; no 'AND-WITH-X' instruction

AND #$72

; High-byte of Address + 1

STA $7133,Y

LDX $02

; restore X-register

PLA

; restore flags and accumulator

```

Note: Memory location \$02 would not be altered by the SHA opcode and it would not use the stack.

#### Test code:

PLP

- general: Lorenz-2.15/shaay.prg, Lorenz-2.15/shaiy.prg

- &{H+1} drop off: CPU/sha/shazpy2.prg CPU/sha/shazpy3.prg CPU/sha/shaabsy2.prg CPU/sha/shaabsy3.prg CPU/sha/shazpy4.prg CPU/sha/shaabsy4.prg

- page boundaries: CPU/sha/shazpy1.prg CPU/sha/shazbsy1.prg CPU/sha/shazpy5.prg CPU/sha/shaabsy5.prg

## Example: SAX abs, y

When using \$FE00 as address, the value stored would be ANDed by \$FF and the SHA turns into a SAX:

SHA \$FE00,Y ; SAX \$FE00,Y

## Example: SAX (zp), y

When using \$FE00 as address, the value stored would be ANDed by \$FF and the SHA turns into a SAX:

LDA #\$FE STA \$03 LDA #\$00 STA \$02

. . .

SHA (\$02),Y ; SAX (\$02),Y

## SHX (A11, SXA, XAS, TEX)

**Type**: Combinations of STA/STX/STY

| Opc. | Mnemonic   | Function           | Size | Cycles | N | ٧ | - | В | D | I | z | С |

|------|------------|--------------------|------|--------|---|---|---|---|---|---|---|---|

| \$9E | SHX abs, y | {addr} = X & {H+1} | 3    | 5      |   |   |   |   |   |   |   |   |

**Operation**: AND X register with the high byte of the target address of the argument + 1. Store the result in memory.

#### **Instabilities**:

- The value written is ANDed with &{H+1}, except when the RDY line goes low in the 4<sup>th</sup> cycle.

- When adding Y to the target address causes a page boundary crossing, the highbyte of the target address is incremented by one (as expected), and then ANDed with X.

Example:

SHX \$6430,Y ;9E 30 64

**Equivalent Instructions:**

PHP ; save flags and accumulator

PHA

$\mathsf{TXA}$

AND #\$65; High byte of Address + 1

STA \$6430, Y

PLA ; restore flags and accumulator

PLP

Note: The SHX opcode would not use the stack.

#### Test code:

- general: CPU/asap/cpu shx.prg, Lorenz-2.15/shxay.prg

- &{H+1} drop off: CPU/shxy/shxy2.prg, CPU/shxy/shxy3.prg, CPU/shxy/shxy4.prg, CPU/shxy/shx-t2.prg, CPU/shxy/shxtest.prg

- page boundaries: CPU/shxy/shxy1.prg, CPU/shxy/shxy5.prg

#### **Simulation links:**

- &{H+1} drop off: http://visual6502.org/JSSim/expert.html? graphics=f&a=0&steps=20&d=a27fa0f39e0211&logmore=rdy&rdy0=15&rdy1=16

- page boundary crossing anomaly: http://visual6502.org/JSSim/expert.html?graphics=f&a=0&steps=18&d=a27fa0f39e0f11

- &{H+1} drop off, plus page boundary crossing anomaly: http://visual6502.org/JSSim/expert.html? graphics=f&a=0&steps=20&d=a27fa0f39e0f11&logmore=rdy&rdy0=15&rdy1=16

# Example: STX abs, y

When using FE00 as address, the value stored would be ANDed by FF and the SHX turns into a STX:

SHX \$FE00,Y ; STX \$FE00,Y

## SHY (A11, SYA, SAY, TEY)

Type: Combinations of STA/STX/STY

| Opc. | Mnemonic   | Function           | Size | Cycles | N | ٧ | - | В | D | I | z | С |

|------|------------|--------------------|------|--------|---|---|---|---|---|---|---|---|

| \$9C | SHY abs, x | {addr} = Y & {H+1} | 3    | 5      |   |   |   |   |   |   |   |   |

**Operation**: AND Y register with the high byte of the target address of the argument + 1. Store the result in memory.

#### **Instabilities**:

- The value written is ANDed with &{H+1}, except when the RDY line goes low in the 4<sup>th</sup> cycle.

- When adding X to the target address causes a page boundary crossing, the highbyte of the target address is incremented by one (as expected), and then ANDed with Y.

Example:

SHY \$7700,X :9C 00 77

**Equivalent Instructions:**

PHP ; save flags and accumulator

PHA TYA

AND #\$78

; High byte of Address + 1

STA \$7700,X

PLA ; restore flags and accumulator

PLP

Note: the SHY opcode would not use the stack.

#### Test code:

- general: CPU/asap/cpu\_shx.prg, Lorenz-2.15/shyax.prg

- &{H+1} drop off: CPU/shxy/shyx2.prg, CPU/shxy/shyx3.prg, CPU/shxy/shyx4.prg

- page boundaries: CPU/shxy/shyx1.prg, CPU/shxy/shyx5.prg

## Example: STY abs, x

When using FE00 as address, the value stored would be ANDed by FF and the SHY turns into a STY:

SHY \$FE00,X ; STY \$FE00,X

## TAS (XAS, SHS)

**Type**: Combinations of STA/TXS and LDA/TSX

| Opc. | Mnemonic   | Function                          | Size | Cycles | N | ٧ | - | В | D | I | Z | С |

|------|------------|-----------------------------------|------|--------|---|---|---|---|---|---|---|---|

| \$9B | TAS abs, y | SP = A & X {addr} = A & X & {H+1} | 3    | 5      |   |   |   |   |   |   |   |   |

**Operation**: This opcode ANDs the contents of the A and X registers (without changing the contents of either register) and transfers the result to the stack pointer. It then ANDs that result with the contents of the high byte of the target address of the operand +1 and stores that final result in memory.

#### **Instabilities**:

- The value written is ANDed with &{H+1}, except when the RDY line goes low in the 4<sup>th</sup> cycle.

- When adding Y to the target address causes a page boundary crossing, the highbyte of the target address is incremented by one (as expected), and then ANDed with (A & X).

```

Example:

TAS $7700,Y ; 9B 00 77

Equivalent Instructions:

; save flags, A, X

PHP

STA $03

; save A

PLA

STA $02

; save flags

; save X

STX $04

LDA $03

; A

AND $04

; and with X

TAX

; remember A & X

AND #$78 ; High-byte of Address